Diseño de circuitos digitales y tecnología de computadores/Sumadores

Semisumador binario (half adder)

[editar]Suma dos bits y proporciona el acarreo.

| Tabla de verdad | Funciones de salida | Circuito combinacional | Bloque funcional | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

Suma: Acarreo (carry): |

|

|

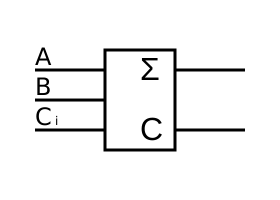

Sumador total (full adder)

[editar]Suma dos bits y el acarreo de entrada de una suma anterior, y proporciona acarreo de salida.

|

Suma: Acarreo de salida (carry output): |

|

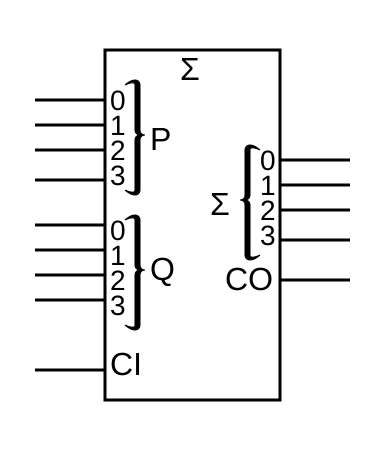

Sumador paralelo de n bits

[editar]Suma dos números binarios de n bits. Consta de una cadena de n sumadores totales conectados a través de sus entradas y salidas de acarreo.

Sumador paralelo de 4 bits con entrada y salida de acarreo |

Bloque funcional sumador de 4 bits (cuádruple sumador total) |

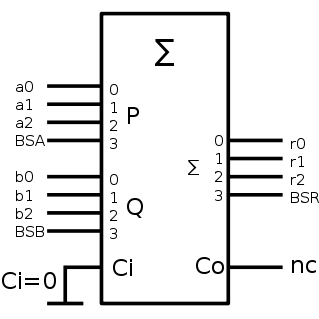

Suma de números enteros

[editar]La forma de realizar la suma de números enteros con signo dependiendo de las diversas formas de representación se expone en el apartado Suma y resta aritméticas. La representación de enteros en signo y magnitud no resulta operativa para la suma de números enteros debido a que requiere operaciones lógicas adicionales y por ello resulta notablemente más compleja que la suma utilizando las representaciones de negativos en complemento a uno (Ca1) o complemento a dos (Ca2). En este apartado veremos sólo los sumadores en Ca1 y en Ca2.

La suma de enteros cuando la representación de negativos es en Ca1 o Ca2 no requiere operaciones adicionales; el resultado se obtiene directamente al realizar la suma de los operandos incluyendo el bit de signo (BS). Esto implica que con un sumador paralelo binario se puede realizar la suma de dos números enteros, cualesquiera que sean sus signos. Únicamente hay que tener en cuenta que en Ca1 hay que sumar el acarreo de salida, mientras que en Ca2 se desprecia el acarreo de salida. Suponiendo una palabra de 4 bits, el bloque funcional sumador de 4 bits se emplearía en cada caso como muestran la figuras siguientes:

|

|

| Sumador en complemento a uno de 4 bits | Sumador en complemento a dos de 4 bits |

El resultado de una suma puede estar fuera del rango de valores admitido por la representación interna de enteros. Un detector de desbordamiento es un circuito combinacional que advierte que el resultado del sumador es inválido. Cuando la representación de enteros es en Ca1 o Ca2, el desbordamiento se detecta cuando existe contradicción entre el bit de signo de los operandos y el bit de signo del resultado:

|

D = BSA·BSB·BSR + BSA·BSB·BSR | ||||||||||||||||