Diseño de circuitos digitales y tecnología de computadores/Biestables

Los biestables son circuitos digitales capaces de almacenar un bit. Constituyen las células de memoria de los sistemas secuenciales. Pueden ser:

- Asíncronos

- Las variables de entrada actúan directamente sobre sobre el sistema e influyen en las variables de salida si se dan las condiciones necesarias.

- Síncronos

- Las variables de entrada actúan sobre el sistema en los instantes en que se activa una entrada de control o sincronismo.

Biestables asíncronos

[editar]Biestable SR

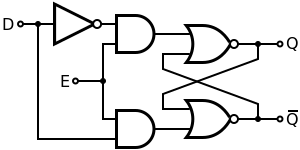

[editar]El biestable SR dispone de dos entradas denominadas R (RESET ≡ poner a 'cero') y S (SET ≡ poner a 'uno'), y dos salidas cuyo estado lógico es opuesto.

|

Bloque funcional | ||||||||||||||||||||||||||||||

El circuito del biestable SR puede realizarse con puertas NOR o NAND. En el circuito con puertas NAND, las entradas S y R son activas a nivel bajo.

|

|

La ecuación del próximo estado es una expresión algebraica que relaciona las entradas con el estado actual para conocer el estado final. La ecuación de próximo estado de un biestable SR viene dada por la siguiente función Qt+1:

|

Qt+1 = S + RQt |

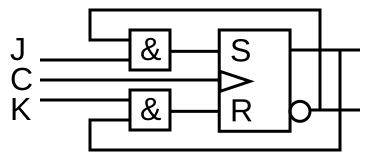

Biestable JK

[editar]El biestable JK aprovecha la combinación prohibida del biestable SR.

|

Bloque funcional |

El biestable JK puede implementarse a partir de un biestable SR:

|

S = JQt R = KQt Ecuación del próximo estado: |

|

Biestables síncronos

[editar]Además de las entradas de información disponen de una entrada de control cuya misión es establecer el instante en el que actúan las entradas de información sobre el biestable.

Los biestables síncronos se clasifican en:

- biestables sincronizados por nivel

- biestables sincronizados por cambio de nivel (flip-flop)

Biestables sincronizados por nivel

[editar]Biestable SR (sincronizado por nivel alto)

[editar]

|

a) Circuito b) Bloque funcional |

La etiqueta C1 representa una dependencia de control con respecto a las entradas R y S; cuando C=0 el biestable no modifica su estado en función de R y S (se inhiben).

Las entradas asíncronas son terminales adicionales sobre el biestable que sirven para establecer su estado de salida con prioridad absoluta, es decir, si están activas se ignora el estado de las otras entradas de información y sincronismo. Normalmente son activas a nivel bajo.

|

|

Bloque funcional |

Biestable D (transparent latch)

[editar]Tiene una única entrada de información. Se utiliza para almacenar un bit.

|

Circuito con puertas NOR |

Bloque funcional |

Biestables sincronizados por cambio de nivel (flip-flops)

[editar]Biestable D maestro-esclavo

[editar]El biestable maestro-esclavo (master-slave) está formado por dos biestables sincronizados por nivel, interconectados por sus terminales de información (la salida del primero con la entrada del segundo) y con sus entradas de sincronismo inversas (se dice que funcionan en contrafase). Al primer biestable se le denomina maestro y al segundo, esclavo, seguidor o subordinado.

La figura siguiente muestra el circuito de un biestable D master/slave.

Cuanto C=0, el maestro está desconectado de su entrada de información (DIN) y el esclavo está habilitado, mostrando en sus salidas (DOUT) el estado del maestro (DMSTR).

Cuando C=1, el esclavo se desconecta del maestro y mantiene el estado de salida (DOUT), mientras que el maestro habilita su entrada de información (DIN).

En el instante en que C cambia de 0 a 1 (flanco descendente), el maestro se desconecta de su entrada de información y el esclavo actualiza su estado, que está determinado por el que posee el maestro. El biestable D master/eslave se comporta como un biestable sincronizado por flanco.

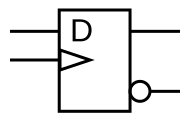

En el símbolo de un biestable D sincronizado por flanco, la entrada de sincronismo se representa mediante un triángulo isosceles. Junto al símbolo de inversión lógica (círculo), indica que el biestable está sincronizado por flanco descendente; en caso contrario (sin círculo), está sincronizado por flanco ascendente:

Sincronizado por flanco ascendente |

Sincronizado por flanco descendente |

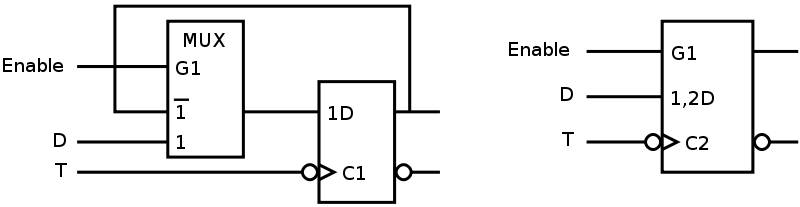

Desinhibición de un flip-flop

[editar]En los sistemas secuenciales, la desinhibición es diferente a la de los combinacionales. Su fórmula es siempre Qt+1=Qt, es decir, se mantiene el estado de salida.

El siguiente ejemplo muestra el circuito de desinhibición del flip-flop D y el bloque funcional correspondiente.

Flip-flop SR (sincronizado por flanco descendente)

[editar]Los esquemas siguientes representan el circuito de un biestable SR de tipo maestro/esclavo sincronizado por flanco descendente y su bloque funcional.

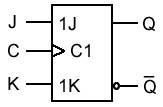

Flip-flop JK (sincronizado por flanco ascendente)

[editar]Tabla de verdad

|

Circuito a partir de un flip-flop SR |

Bloque funcional |

Flip-flop T

[editar]Equivale a un flip-flop JK con las entradas J y K unidas.